# Technology and model parameters

VDD = 1.8 # Supply voltage [V]

VTHN = 0.4 # NMOS threshold voltage [V]

VTHP = -0.4 # PMOS threshold voltage [V]

mu_n_Cox = 200e-6 # NMOS process transconductance parameter [A/V^2]

mu_p_Cox = 100e-6 # PMOS process transconductance parameter [A/V^2]

lambda_n = 0.1 # Channel length modulation NMOS [1/V]

lambda_p = 0.1 # Channel length modulation PMOS [1/V]6 IC Design of a Universal Biquad Filter

This project explores the IC design of a biquad filter from mathematical modelling over ideal circuit implementations to sizing and using several differnet OTAs and a concluding physical implementation of an OTA. Two different OTA models were incorporated into implementing the universal biquad filter and compared with simulations to the theoretical model. Additionally, a low pass filter was designed with a Gm-C filter to try to realise the required behauviour that way. To experience the the actual physical layouting of an IC chip, the 5T-OTA was implemented as a physical design with the help of KLayout. GitHub Repo

7 Introduction

This chapter provides a short motivation and overview for the IC design process done during the lecture “Analogue and Mixed-Signal Circuit Design” that Prof. Dr.-Ing. M. Meiners gives in the graduate course Electronic Engineering M.Sc. at City University of Applied Sciences Bremen.

The chapter will start with the motivation behind the biquad IC filter design, outline the scope of work of the project, and ends with giving concrete specifications for the implemented filter.

7.1 Motivation

The design and implementation of analog filters is a cornerstone in signal processing, with applications ranging from audio processing to communication systems. Among these, second order filters, like the biquad filter, are versatile building blocks due to its ability to realize four types of second order filters - low pass, high pass, band pass, and band stop. This project focuses on the integrated circuit (IC) design of a biquad filter, to get insight into the theoretical and practical engineering considerations behind IC design.

For a deeper understanding of IC design, this project does not rely on off-the-shelf operational amplifiers for the filter design, but aims to implement the entire filter architecture at the transistor level. This approach not only deepens the understanding of analog filter behavior but also introduces the challenges and intricacies of IC design, such as layout constraints, power efficiency, and stability.

This project demonstrates the design process of IC design from theorectical modelling, over simulation and design constraints to prototyping and to learn hands-on experience with tools used during the design process.

7.2 Scope of the project

The scope of this project is supposed to follow a real-world design flow, starting at a theorectical analysis of the specified filter and - in the best case - end in a tape-out of a prototype. If that stage is reached the prototype can be compared to the theorectical and simulation results obtained during the design process and checked for functionality.

As a tape-out of a prototype is fairly unrealistic in the time given, the goal is to simulate the specified filter with templates for operational amplifiers and base the IC layout on these templates.

All in all, this project includes a systems analysis if the specified filter, simulation results with ideal components and real components, taken from provided templates, and a physical layout prototype.

7.3 Specifications

The main objective is to design a universal biquad filter, based on the filter design proposed in the ASLK PRO Board Manual from Texas Instruments [1]. The biquad filter shall have the following specifications:

\[ f_0 = 1\,kHz \]

\[ Q = 10 \]

The circuit design is done in Xschem and the simulation in ngspice. For the design on transistor level the 130nm CMOS technology SG13G2 is used. All these tools and PDk are integrated into a docker image IIC-OSIC-TOOLS [2] provided by Prof. Dr. Harald Pretl from Johannes Keplar University, Linz, Austria

This documentation provides a development report, which documents the design process with the taken steps and decisions made.

7.4 Open-Source

All the results of this report and development approach to design a Biquad will be publicly available on GitHub. Everyone is invited and should feel free to use, change, and share this work. This whole course and project wouldn’t be possible without the great Open-Source tools provided by the amazing community of layout designers, enthusiasts, and developers. Here is a list with just a few of these programs: IC-OSIC-TOOLS, IHP Open PDK, Linux, Docker, Xschem, ngspice, KLayout, Quarto, Vim, Pandoc, LaTeX, TeXLive, Python, Git, CoCalc, LibreOffice.

7.4.1 Anthem

In realms where code is free to fly,

We build and share, our hearts reach high.

No walls, no locks, our wisdom streams,

In open light, we chase our dreams.

So sing the joy, the thrill, the spark,

In open source, we find our arc.

Together strong, we rise, explore—

In lines of code, forevermore.

8 Theoretical Background

This chapter introduces the theory and core concepts necessary for IC design of a biquad filter. It is structured in a way, that it goes from the big picture to the small components. First, biquad filters are introduced with a focus on the universal biquad filter. After that, operational amplifiers come into the the foreground, as biquad filters make use of them in their circuits. Operational amplifiers are looked upon from an IC design standpoint.

8.1 Biquad filter

The biquadratic filter, also known as the biquad filter, has its earliest implementation in the 1960s but is still in use today, most commonly in radio frequency receivers [3]. In its application in RF-technology, it is used to remove unwanted neighboring signals ans noise [4]. As biquad filter are second-order filters, they are also used as building blocks for higher filter implementations, by cascading them and adding first order filters [1].

8.1.1 Universal biquad filter

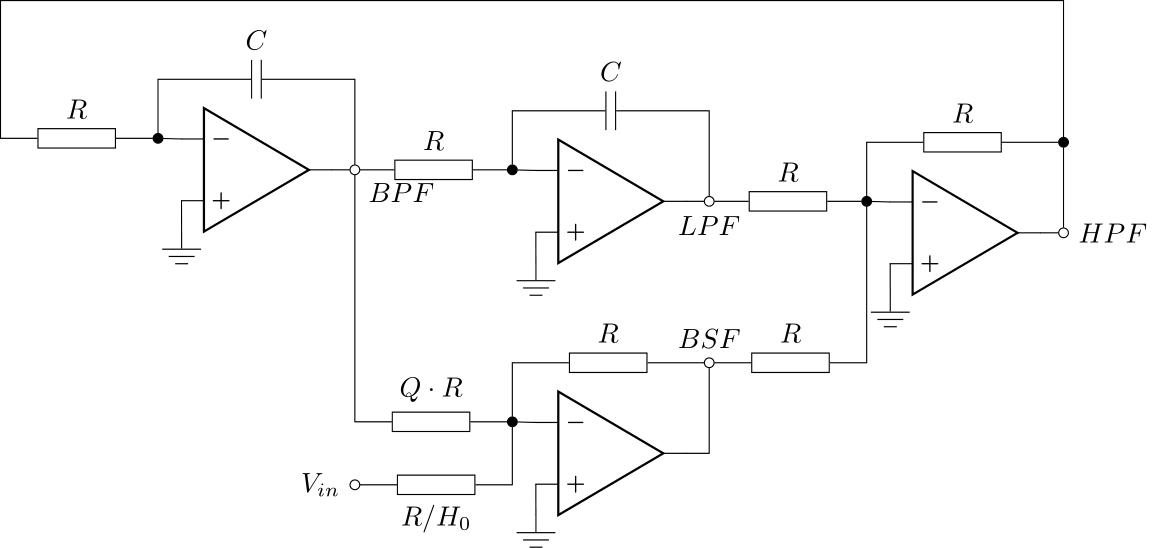

For the filter design in this project, an universal biquad filter is used. The universal biquad filter is biquad filter variant with four operational amplifiers used in its design and the property of being able to be used in four different filter variants. Depending on the output of the universal biquad used, a low pass filter, high pass filter, band pass filter, or band stop filter will be implemented. This can be seen in Figure 8.1. [1]

The universal biquad filter consists of two non-inverting amplifiers working as adders in the circuit and two integrators. By setting \(R\) and \(C\) to specific values, the resonance frequency can be chosen. Other parameters adjustable in the universal biquad filter are the quality factor \(Q\) and the low-frequency gain \(H_0\). The quality factor and low-frequency gain determine the frequency response peaks of the low pass filter and the band pass filter. [1]

8.1.2 Characteristics

As the universal biquad filter is a second order filter with the specified outputs low pass, high pass, band pass, and band stop, each filter option can be described with a tranfer function on system level. The general second order transfer function is:

\[ H(s) = \frac{a_1 s^2 + b_1 s + c_1}{a_2 s^2 + b_2 s + c_2} \tag{8.1}\]

The coeffcients can be choosen so, that different responses, like low pass, high pass, band pass, and band stop are achieved.

In filter design a variant of this generalized transfer function is often choosen because it is easier describe the system by quality factor and angular frequency. Equation 8.2 is an exemplatory low pass filter with a transfer function specified for filter design. [3]

\[ H(s) = \frac{\omega_n^2}{s^2 + \frac{\omega_n}{Q} s + \omega_n^2} \tag{8.2}\]

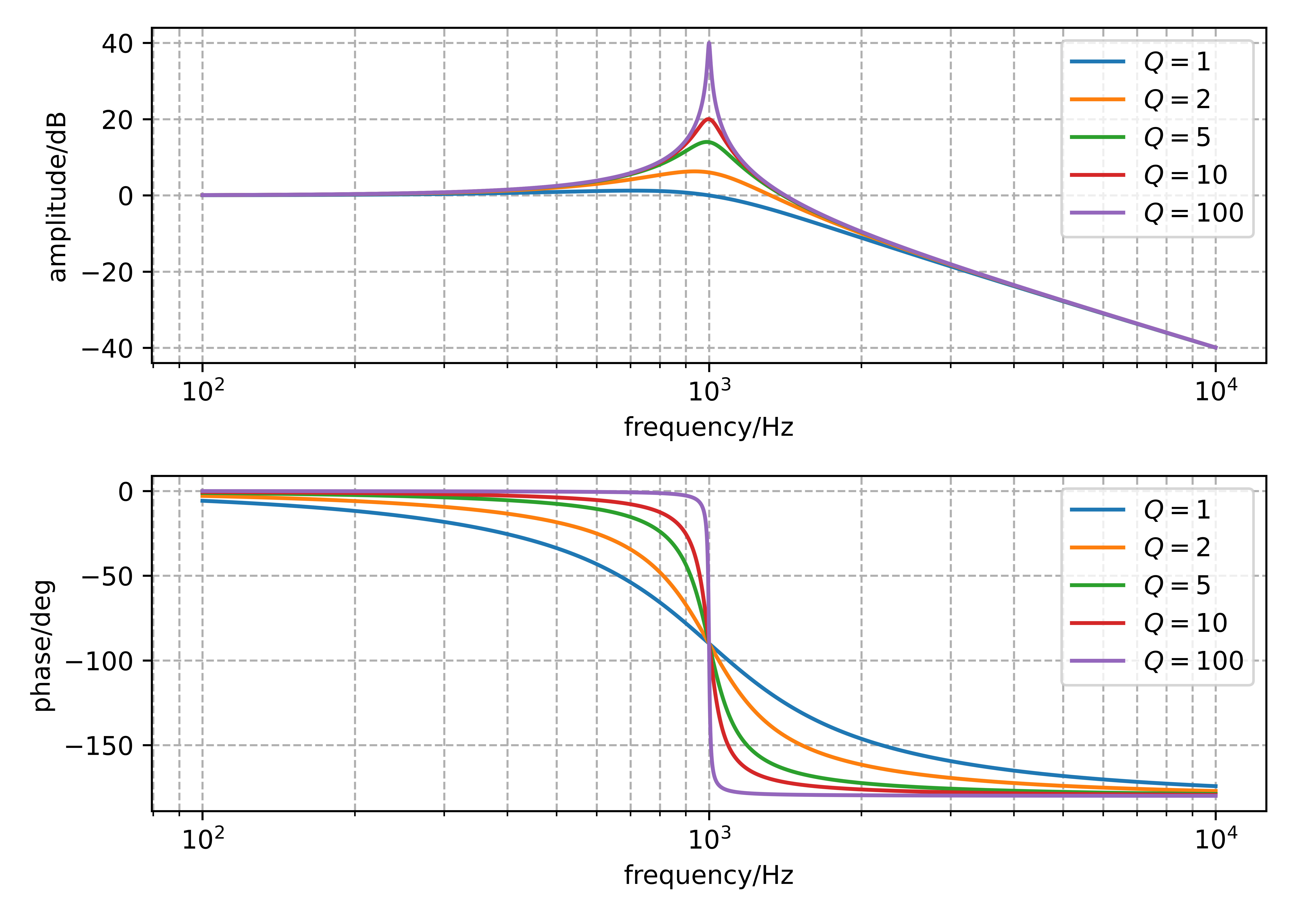

\(Q\) determines amoung other things the amount of peaking the transfer function has at the chosen frequency. Figure 8.2 shows this graphically, the amout of peaking increases with increasing quality factor \(Q\).

Code

# Behavioral Analysis Biquad Filter

import numpy as np

import matplotlib.pyplot as plt

# Initial values

f0 = 1e3 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q1 = 1 # Quality factor

Q2 = 2

Q3 = 5

Q4 = 10

Q5 = 100

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(2, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

#b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

#b_bp = (-H0 * (s / w0))

# Band Stop Filter

#b_bs = -((1 + (s**2 / (w0**2))) * H0)

# Denominator -> for all filters the same

a0 = 1

a1_1 = (s / (w0 * Q1))

a1_2 = (s / (w0 * Q2))

a1_3 = (s / (w0 * Q3))

a1_4 = (s / (w0 * Q4))

a1_5 = (s / (w0 * Q5))

a2 = (s**2 / (w0**2))

den1 = a0 + a1_1 + a2

den2 = a0 + a1_2 + a2

den3 = a0 + a1_3 + a2

den4 = a0 + a1_4 + a2

den5 = a0 + a1_5 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp_1 = b_lp / den1

Hs_lp_2 = b_lp / den2

Hs_lp_3 = b_lp / den3

Hs_lp_4 = b_lp / den4

Hs_lp_5 = b_lp / den5

#Hs_hp = b_hp / den

#Hs_bp = b_bp / den

#Hs_bs = b_bs / den

# Bode Diagram

fig, axs = plt.subplots(2)

#fig.suptitle("frequency response of biquad filter")

# Low Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp_1)), label='$Q = 1$')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp_1)) * (180 / np.pi), label='$Q = 1$')

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp_2)), label='$Q = 2$')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp_2)) * (180 / np.pi), label='$Q = 2$')

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp_3)), label='$Q = 5$')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp_3)) * (180 / np.pi), label='$Q = 5$')

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp_4)), label='$Q = 10$')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp_4)) * (180 / np.pi), label='$Q = 10$')

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp_5)), label='$Q = 100$')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp_5)) * (180 / np.pi), label='$Q = 100$')

'''

# High Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='high pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_hp)) * (180 / np.pi), label='high pass')

# Band Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='band pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_bp)) * (180 / np.pi), label='band pass')

# Band Stop Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='band stop')

axs[1].semilogx(frequencies, (np.angle(Hs_bs)) * (180 / np.pi), label='band stop')

'''

#axs[0].title("amplitude response")

axs[0].set_xlabel("frequency/Hz")

axs[0].set_ylabel("amplitude/dB")

#axs[0].set_ylim(-50, 25)

axs[0].grid(True, which="both", ls="--")

axs[0].legend(loc=1)

#axs[1].title("phase response")

axs[1].set_xlabel("frequency/Hz")

axs[1].set_ylabel("phase/deg")

axs[1].grid(True, which="both", ls="--")

axs[1].legend()

plt.tight_layout()

#plt.show()

plt.savefig('images/sec_theorectical_background/lowPassDifferentQ.png', format='png', dpi=1000)

The height of the peak can be calculated with:

\[ A_{peak} = \frac{Q}{\sqrt{1 - \frac{1}{4Q^2}}} \tag{8.3}\]

For \(Q = 100\) the peak is \(A_{peak} = 100.001\), which converted into dB is \(A_{peak,dB} = 40\,dB\), as is shown in Figure 8.2.

8.2 Operational Amplifier

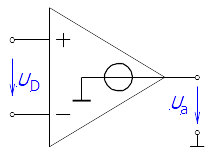

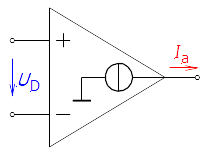

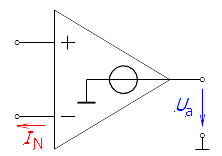

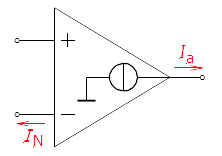

As seen in Figure 8.1, a Biquad Filter consists of four Operational Amplifiers. To get a better understanding of these, this chapter will discuss the main aspects of OPAMPs. There are different types of operational amplifiers that differ, for example, by their low- or high-impedance inputs and outputs. According to Schmid, there exist nine different types of the Opamps, but only four are mainly used [5]. This is because almost always, the non-inverting (positive) input is designed as a high-impedance voltage input. The inverting (negative) input can either be a high-impedance voltage input or a low-impedance current input, depending on the type. Accordingly, the output can be either a low-impedance voltage output or a high-impedance current output. This results in four basic configurations, as shown in the accompanying table Table 8.1. (Images are taken from [6])

| Voltage output | Current output | |

|---|---|---|

| Voltage input | Voltage-Feedback Amplifiers | Operational Transconductance Amplifier |

|

|

|

| Current input | Current-Feedback Amplifiers | Current Amplifier |

|

|

As a general rule, the simplest circuit that can do a job is usually the best choice. [7]

8.2.1 Voltage-Feedback Amplifiers (VFA)

When discussing operational amplifiers (OPAMPs), most sources refer to the Voltage-Feedback Amplifier. These VFAs are voltage-controlled voltage sources, essentially acting as voltage boosters. They are characterized by a high-impedance input for both the non-inverting and inverting terminals, and a low-impedance voltage output. To realize various desired circuits, such as amplification, integration, addition/subtraction, etc…, these functions should ideally be achieved only through the surrounding circuitry. To meet this requirement, three main requirements need be satisfied:

- Extremely High Voltage Gain: Typically ranging from 60 to 120 dB (or gain factor of \(10^4\) to \(10^6\)), this gain should be available over a wide frequency range.

- High Impedance at Differential Inputs: Ensuring minimal loading of the signal source.

- Low Impedance at the Output: Allowing the amplifier to drive various loads without significant voltage drop.

Voltage source

A voltage source creates a constant voltage output by changing the current.

Current source A current source creates a constant current by changing the voltage.

Both of this sources can be explained by Ohm’s Law: \(R = \frac{U}{I}\).

For example the voltage source: There is no influence of the load, so \(R\) may change and its value is unknown to the source. So to keep the voltage stable we can only change the current.

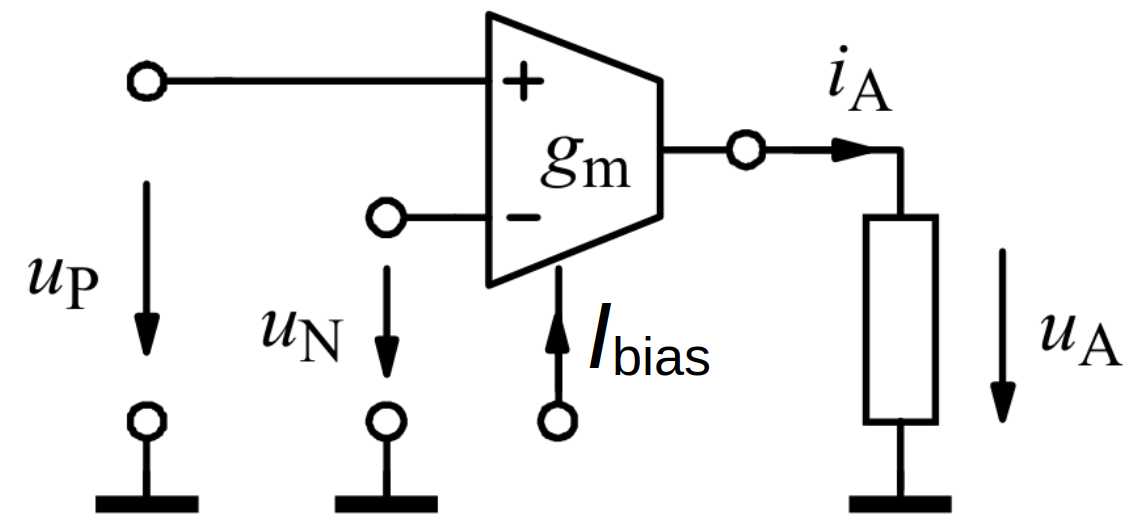

8.2.2 Operational Transconductance Amplifier (OTA)

In the design process of the biquad only OTAs will be used, so the focus of this chapter will be on them. The operational transconductance amplifier puts out out a current proportional to its input voltage, unlike Voltage Feedback Amplifiers Section 8.2.1. In other words, an OTA is a voltage controlled current source.

As seen in the figure Figure 8.3, the OTA has the two differental inputs and a current output. On top of that it has a biasing current input \(I_{bias}\) which controls the transconductance \(g_m\) of the OTA.

8.2.2.1 Transconductance

Transconductance is a fundamental parameter that describes the relationship between the input voltage and the output current in electronic devices, particularly in transistors. It is defined as the ratio of the change in output current to the change in input voltage, under conditions where all other variables are held constant. Mathematically, it is expressed as:

\[ g_m = \frac{\Delta I_{out}}{\Delta V_{in}} \]

where \(g_m\) is the transconductance, \(\Delta I_{out}\) is the change in output current, and \(\Delta V_{in}\) is the change in input voltage. The unit of transconductance is the siemens (\(S\)), which is equivalent to amperes per volt (\(A\)/\(V\)). Historically, it was also measured in “mho”, which is “ohm” spelled backwards, reflecting its inverse relationship to resistance.

In field-effect transistors (FETs) the transconductance determines the device’s ability to amplify signals. A higher transconductance value indicates a stronger amplification capability, as a small change in input voltage can result in a significant change in output current.

The term transconductance originates from the concept of transfer conductance. It combines the ideas of transfer, indicating the transfer of a signal from the input to the output, and conductance, which is the inverse of resistance and measures how easily a material conducts electric current. In essence, transconductance describes how effectively a device can convert a voltage change at its input into a proportional current change at its output. [9]

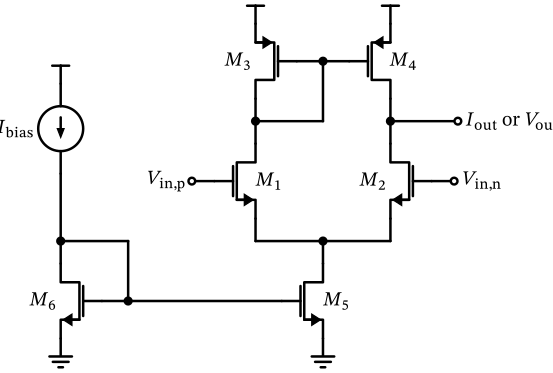

8.2.2.2 5-Transistor OTA

[7] introduces a basic 5-Transistor OTA as a design proposal for a real circuits.

It consists of few elements which are going to be described in the next chapters. The basic function of this OTA can be described with: The transistors \(M_1\) and \(M_2\) form a differential pair, which is biased by the current source \(M_5\). Transistors \(M_5\) and \(M_6\) create a current mirror, where the input bias current \(I_{\text{bias}}\) sets the bias current for the Operational Transconductance Amplifier. To keep the biasing current stable, a current mirror (Section 8.2.3) is used instead of applying the \(I_{\text{bias}}\) directly to \(M_5\). The differential pair (Section 8.2.4) \(M_1\) and \(M_2\) is loaded by the current mirror \(M_3\) and \(M_4\), which mirrors the drain current of \(M_1\) to the right side of the circuit. The combined currents from \(M_4\) and \(M_2\) at the output node result in the generation of an output current. To achieve this desired result, it is important to ensure that \(M_{1,2}\) and \(M_{3,4}\) are symmetric, meaning they should have identical \(W\) (width) and \(L\) (length) dimensions. To set the right bias current, \(M_{5,6}\) should be chosen accordingly.

8.2.3 Current Mirror

A current mirror consists of at least two transistors, one working as the input (reference) source and the other ones as copies of it. As the name suggests, the primary function of a current mirror is to copy the input current to the output, ensuring that the output current is an exact duplicate of the input. Importantly, the flow of the input current is unaffected by the size of the mirrored output current or any variations in it.

This behavior is made possible by two key characteristics of the current mirror: its relatively low input resistance and its relatively high output resistance. The low input resistance ensures the input current remains stable regardless of drive conditions, and the high output resistance maintains a constant output current independent of load variations. ([11])

A current mirror is also capable of copying one current and converting it to multiple different outputs. This is possible by attaching more transistors with their gate \(G\) to the drain \(D\) of the reference transistor. By scaling the width and length of each output transistor differently, multiple scales of the input current can be created. Hereby, a big advantage is when using MOSFETs, due to the fact that no current is flowing through the gate. In the case of BJTs, a compensation circuit is added. ([7])

8.2.4 Differential Pair

A differential pair, also referred to as a differential amplifier, is an electronic circuit designed to compare the difference between two input voltages while minimizing any voltage that is common to both inputs. It consists of two transistors and can have two inputs and two outputs, as seen in Figure 8.6.

Its primary function is to amplify the difference between two input signals while rejecting any common-mode signals, which are identical in both amplitude and phase at the two inputs. This property makes the differential pair highly effective in noise reduction and signal processing applications. In a typical differential pair using MOSFETs, the two transistors are matched in terms of their electrical characteristics, such as threshold voltage \(V_{th}\) and transconductance \(g_m\). The inputs are applied to the gates \(G\) of the MOSFETs, while the outputs are taken from the drains \(D\). A current source is usually connected to the sources \(S\) of the MOSFETs to provide a constant bias current, here noted as \(g_{\text{tail}}\) or like in Figure 8.4 as \(I_{\text{bias}}\).

The differential gain of the pair is determined by the transconductance \(g_m\) of the MOSFETs. The common-mode rejection ratio (CMRR) is a measure of the differential pair’s ability to reject common-mode signals. It is defined as the ratio of the differential gain to the common-mode gain and is typically expressed in decibels (dB). The performance of the differential pair is also influenced by the tail current source, represented by \(g_{\text{tail}}\). The tail current source provides a constant bias current \(I_{\text{bias}}\) that flows through both transistors, ensuring that the total current through the differential pair remains constant regardless of the input voltages. ([4])

When used in OTAs, the differential pair serves as the input stage, where the differential input voltage is converted into a differential current.

8.3 MOSFET (Metal-Oxide-Semiconductor Field-Effect-Transistor )

To dive in one more level, the parts an operational amplifier is build of are transistors. Precisely in this design process they are (MOSFETs). In integrated circuit design, where pre-built components are not available, MOSFETs can be designed from scratch. This design flexibility allows for the adjustment of the MOSFET’s physical dimensions, specifically its width \(W\) and length \(L\). By doing this there is a lot of room for freedom and experimental space. The length \(L\) significantly influences MOSFET performance, enabling a trade-off between speed and output conductance. The width \(W\) of a MOSFET acts as a scaling factor that adjusts the charge density within the channel, enabling the control of current levels to meet specific design requirements.

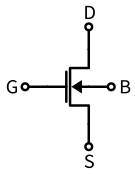

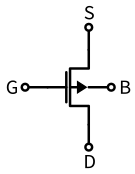

In the literature, the circuit symbol of MOSFETs is not uniform. Some denote them with a small arrow between the gate (\(G\)) and source (\(S\)), which is not very precise due to the fact MOSFETs are symmetric. This means that the drain (\(D\)) and source (\(S\)) can be interchanged, and the names are only defined to make circuits clearer. Therefore, an accurate symbol for the n-MOS (shown in Figure 8.7) and p-MOS (shown in Figure 8.8) is shown in the following figures taken from [7]:

However, in this development report, the symbols are not strictly used like shown here. But all of the used figures are based on this symmetric model of a MOSFET.

Besides, in many situations the bulk \(B\) is connected to the source \(S\) terminal. Thus the bulk \(B\) is not mentioned in the circuit diagrams.

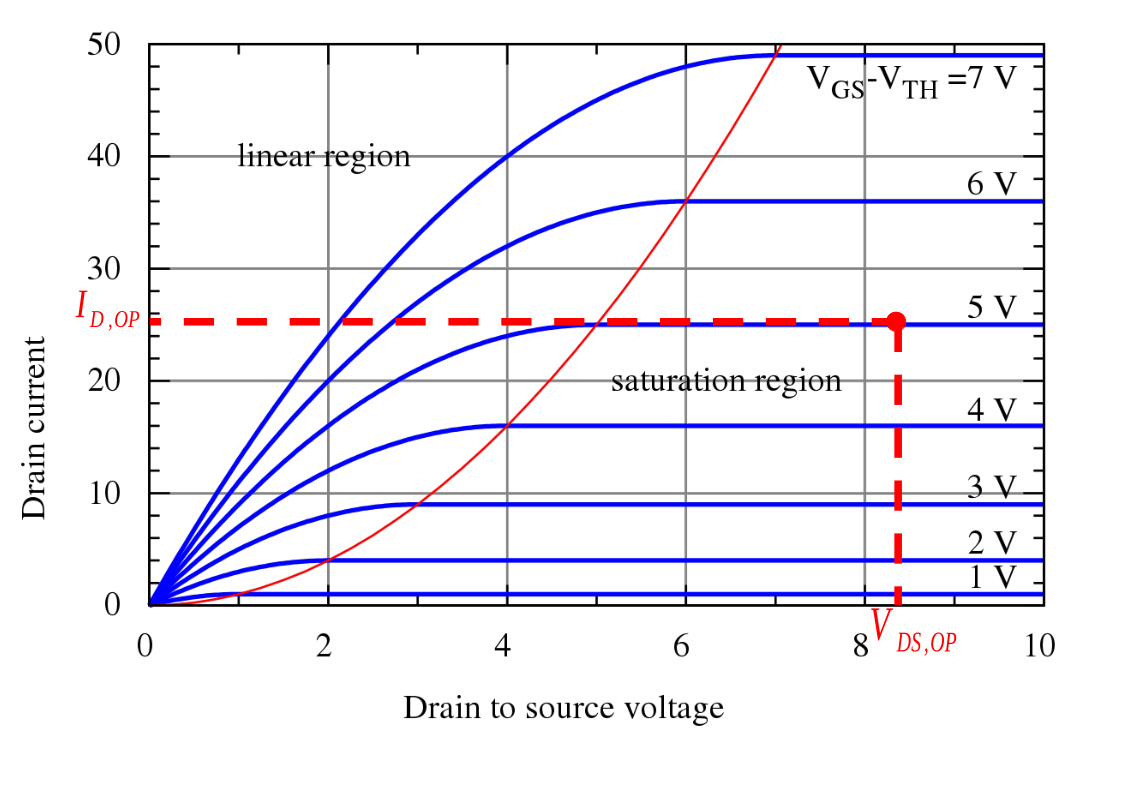

8.3.1 MOSFET Large-Signal Regions

A MOSFET can operate in three different modes: Saturation, Linear (or Triode) region, or Cutoff. The modes depend on the device’s threshold voltage \(V_{\text{th}}\), gate-to-source voltage \(V_{\text{GS}}\), and drain-to-source voltage \(V_{\text{DS}}\).

Saturation

The saturation region is the active mode used for analog amplification, where the MOSFET behaves like a voltage-controlled current source. A conductive channel forms between the source and drain. This state is reached when the condition \(V_{\text{DS}} \geq (V_{\text{GS}} - V_{\text{th}})\) is met. In saturation, the drain-source current (\(I_D\)) stabilizes or “saturates” and becomes nearly independent of \(V_{\text{DS}}\). However, it can still be precisely controlled via \(V_{\text{GS}}\) due to the phenomenon known as “pinch-off”.

Linear Region

The Linear, or Triode, region occurs when a MOSFET is conducting and acts more like a resistor or voltage-controlled device rather than a current source. This region is defined by the condition \(V_{\text{DS}} < (V_{\text{GS}} - V_{\text{th}})\) and \(V_{\text{GS}} > V_{\text{th}}\). In this mode, both \(V_{\text{GS}}\) and \(V_{\text{DS}}\) control the \(I_D\), allowing the device to be used effectively for switching and amplification in low-voltage applications.

Cutoff Region

In the cutoff region, the MOSFET is effectively turned off, with no conductive channel formed between the drain and source. This mode is reached when the gate-to-source voltage is less than the threshold voltage (\(V_{\text{GS}} < V_{\text{th}}\)). In cutoff, the drain-source current \(I_D\) is nearly zero, which means the MOSFET is not conducting and behaves like an open switch.

In the large-signal analysis, the transitions between operating modes occur gradually, making it challenging to pinpoint an exact moment when one mode shifts to another. Consequently, the modes are used in a more approximate manner, reflecting the continuous nature of these transitions rather than distinct, sharply defined states.

8.3.2 Small-Signal Representation

By applying different voltages to a MOSFET, different behaviours appear. But there is one thing which is very unliked by engineers and others, all these transfer functions are non linear. So making any calculations by hand is nearly impossible. That’s why in practise the biasing method exists. This is done by applying a dc voltage to the terminals of the MOSFET and during operation only a small signal change appears. With this technique an Operating Point is created, which enables to assume a linear behaviour in its small signal area (like in Figure 8.9). Because the MOSFET is put into an small operation point and all the changes applied are very small, this linearisation area is called Small-signal model.

- \(I_D\): The drain current

- \(I_{\text{bias}}\): The biasing current. The current to adjust the operating point

- \(V_{GS}\): The gate-to-source voltage

- \(V_{DS}\): The drain-to-source voltage

- \(V_{th}\): The threshold voltage. A critical parameter that defines the minimum gate-to-source voltage \(V_{GS}\) required to form a conductive channel between the source and drain

- \(V_{OV}\): The overdrive voltage. the difference between the gate-to-sourcevoltage \(V_{GS}\) and the threshold voltage \(V_{th}\).

- \(g_m\): The transconductance. The ratio between the output current and input voltage

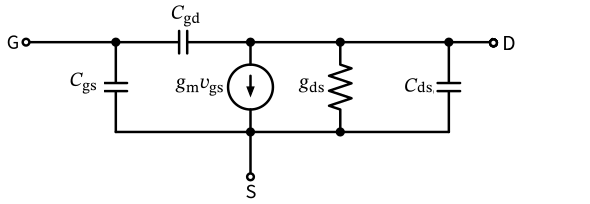

8.3.2.1 Capacitances in MOSFETs

Gate-Source Capacitance (\(C_{gs}\)):

\(C_{gs}\) is the capacitance between the gate and source terminals. This arises due to the physical overlap of the gate and source regions, as well as the insulating oxide layer between them. \(C_{gs}\) affects both the input impedance and the switching speed. Higher \(C_{gs}\) values can slow down the switching process because more charge needs to be moved to change the gate voltage.

Gate-Drain Capacitance (\(C_{gd}\)):

\(C_{gd}\) is the capacitance between the gate and drain terminals. People also know it as the Miller capacitance because of its significant impact on the Miller effect. The Miller effect amplifies the effective value of \(C_{gd}\), making it a critical factor in determining the high-frequency behaviour of the MOSFET. This capacitance can cause phase shifts and affect the stability of the circuit, particularly in amplifiers.

Drain-Source Capacitance (\(C_{ds}\)):

\(C_{ds}\) is the capacitance between the drain and source terminals. It arises due to the depletion region between the drain and source regions. \(C_{ds}\) affects the output impedance and frequency response of the circuit. Higher drain-source capacitance can lead to increased output capacitance, affecting the switching speed and introducing additional losses.

8.3.2.2 Transconductances in MOSFET

Output Conductance (\(g_{ds})\)

\(g_{ds}\) represents the small-signal conductance between the drain and source terminals of the MOSFET. It expresses how the drain current \(I_D\) changes with respect to the drain-source voltage \(V_{ds}\) when the gate-source voltage \(V_{gs}\) is held constant. Mathematically, it is defined as follows:

\(g_{ds}=\frac{\partial I_D}{\partial V_{ds}}\bigg|_{V_{gs}=\text{constant}}\)

\(g_{ds}\) affects the output impedance of the MOSFET. A higher \(g_{ds}\) results in a lower output impedance.In saturation region, \(g_{ds}\) is typically small, which helps maintain the linearity of the device. However, in the triode region, \(g_{ds}\) can be larger, leading to non-linear behaviour.

Mutual Transconductance - Gate-Source Voltage (\(g_mv_{gs}\))

The transconductance \(g_m\) of a MOSFET quantifies how the drain current \(I_D\) varies in response to changes in the gate-source voltage \(V_{gs}\), while keeping the drain-source voltage \(V_{ds}\) constant:

\(g_m=\frac{\partial I_D}{\partial V_{gs}}\bigg|_{V_{ds}=\text{constant}}\)

The term \(g_mv_{gs}\) represents the small-signal current generated by the transconductance \(g_m\) in response to a small change in the gate-source voltage \(v_{gs}\). A higher \(g_m\) results in a higher voltage gain.

In the saturation region, the output conductance \(g_{ds}\) is generally much smaller than the transconductance \(g_m\). This characteristic enables the MOSFET to function effectively as a voltage-controlled current source. However, as the MOSFET moves into the triode region, \(g_{ds}\) increases, causing the device to behave more like a resistor. The output conductance \(g_{ds}\) influences the output impedance and linearity of the device, while the product \(g_mv_{gs}\) controls the gain and frequency response of the circuit.

9 Characterisation

This chapter is about characterising the biquad filter with the help of computational software like python and and comparing that with ideal circuit simulations. The comparison between a mathematical approach and a basic circuit implementation, gives a first impression if the filter is operational.

9.1 Behauvioural Analysis and macro modelling

The behauvioural analysis is done through macro modelling the universal biquad filter as a system. The system can be described with transfer functions and modelled with python.

9.1.1 Transfer Functions and frequency response

The ASLK PRO Manual [1] provides the transfer functions of the four filter outputs: low pass, high pass, band pass, and band stop. The transfer functions are adaptations of the general second order transfer function as seen in Equation 8.1. [3]

In the following transfer function the input and output voltage are referenced according to Figure 8.1. The sections only contain their specific transfer function and frequency response.

Low pass

The output if the low pass filter is marked in the circuit (Figure 8.1) as \(LPF\) and corresponds to \(V_{03}\) in the transfer function Equation 9.1.

\[ \frac{V_{03}}{V_i} = \frac{H_0}{\left( 1 + \frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2} \right)} \tag{9.1}\]

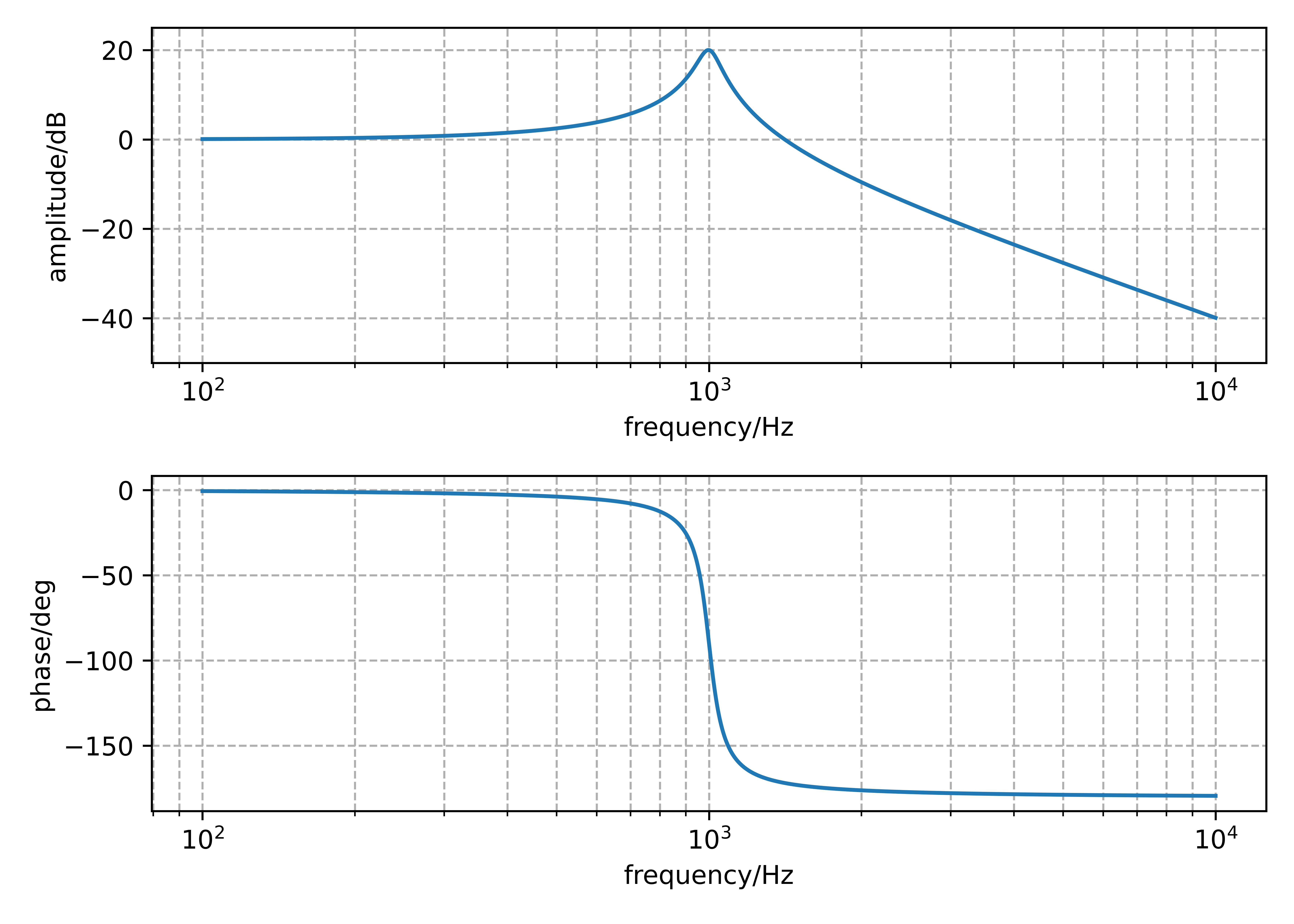

Figure 9.1 shows the amplitude and phase response of the low pass filter. The required frequency \(f_0 = 1\,kHz\) and quality factor \(Q = 10\) recognizable in the bode plot. As the dc-gain was chosen to be \(H_0 = 1\), the low pass filter has a amplitude amplification of 1 in the lower frequencies.

#| label: lst-freqResponseLowpass

#| code-fold: true

#| output: false

# Behavioral Analysis Biquad Filter

import numpy as np

import matplotlib.pyplot as plt

# Initial values

f0 = 1e3 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(2, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -((1 + (s**2 / (w0**2))) * H0)

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

# Bode Diagram

fig, axs = plt.subplots(2)

#fig.suptitle("frequency response of biquad filter")

# Low Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp)), label='low pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp)) * (180 / np.pi), label='low pass')

'''

# High Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='high pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_hp)) * (180 / np.pi), label='high pass')

# Band Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='band pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_bp)) * (180 / np.pi), label='band pass')

# Band Stop Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='band stop')

axs[1].semilogx(frequencies, (np.angle(Hs_bs)) * (180 / np.pi), label='band stop')

'''

#axs[0].title("amplitude response")

axs[0].set_xlabel("frequency/Hz")

axs[0].set_ylabel("amplitude/dB")

axs[0].set_ylim(-50, 25)

axs[0].grid(True, which="both", ls="--")

#axs[0].legend(loc=1)

#axs[1].title("phase response")

axs[1].set_xlabel("frequency/Hz")

axs[1].set_ylabel("phase/deg")

axs[1].grid(True, which="both", ls="--")

#axs[1].legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/freqResponseLowpass.png", format="png",dpi=1000)

With knowing the dc gain \(H_0 = 1\) and quality factot \(Q = 10\), the amplitude of the peak can be calculated as seen in Equation 8.3. Expression the value in dB, gives peak amplitude of \(A_{peak,dB} = 20.002\,dB\) which corresponds to the peak value seen in Figure 9.1.

High pass

The output if the high pass filter is marked in the circuit (Figure 8.1) as \(HPF\) and corresponds to \(V_{01}\) in the transfer function Equation 9.2.

\[ \frac{V_{01}}{V_i} = \frac{\left( H_0 \cdot \frac{s^2}{\omega_0^2} \right)}{\left( 1 + \frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2} \right)} \tag{9.2}\]

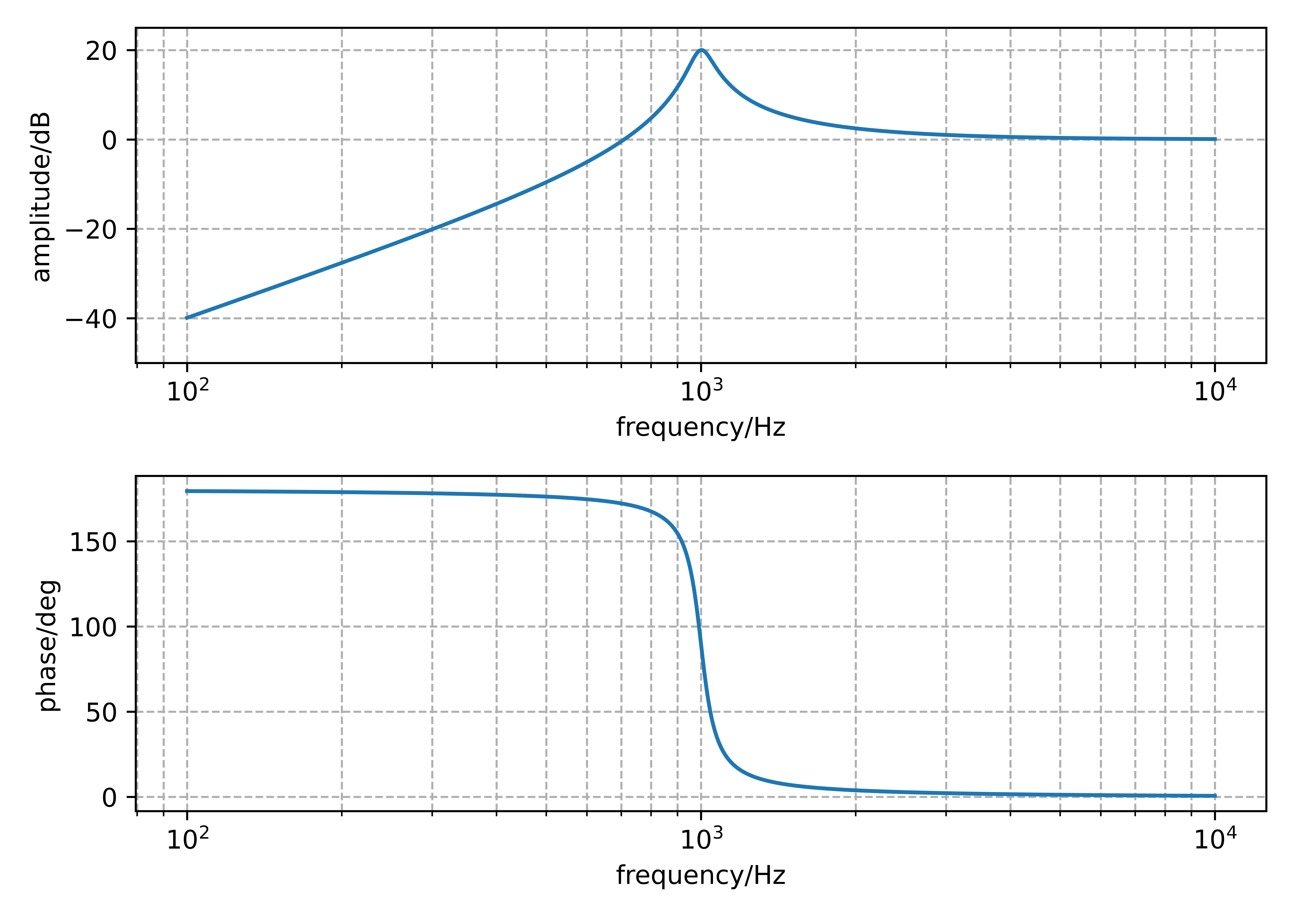

Figure 9.2 shows the amplitude and phase response of the high pass filter. The required frequency \(f_0 = 1\,kHz\) and quality factor \(Q = 10\) recognizable in the bode plot. As the dc-gain was chosen to be \(H_0 = 1\), the low pass filter has a amplitude amplification of 1 in the higher frequencies.

#| label: lst-freqResponseHighpass

#| code-fold: true

#| output: false

# Behavioral Analysis Biquad Filter

import numpy as np

import matplotlib.pyplot as plt

# Initial values

f0 = 1e3 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(2, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -((1 + (s**2 / (w0**2))) * H0)

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

# Bode Diagram

fig, axs = plt.subplots(2)

#fig.suptitle("frequency response of biquad filter")

# Low Pass Filter

#axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp)), label='low pass')

#axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp)) * (180 / np.pi), label='low pass')

# High Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='high pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_hp)) * (180 / np.pi), label='high pass')

'''

# Band Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='band pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_bp)) * (180 / np.pi), label='band pass')

# Band Stop Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='band stop')

axs[1].semilogx(frequencies, (np.angle(Hs_bs)) * (180 / np.pi), label='band stop')

'''

#axs[0].title("amplitude response")

axs[0].set_xlabel("frequency/Hz")

axs[0].set_ylabel("amplitude/dB")

axs[0].set_ylim(-50, 25)

axs[0].grid(True, which="both", ls="--")

#axs[0].legend(loc=1)

#axs[1].title("phase response")

axs[1].set_xlabel("frequency/Hz")

axs[1].set_ylabel("phase/deg")

axs[1].grid(True, which="both", ls="--")

#axs[1].legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/freqResponseHighpass.png", format="png", dpi=1000)

Band pass

The output for the band pass filter is marked as \(BPF\) in Figure 8.1. This denotes the point that is referenced in Equation 9.3 as \(V_{02}\).

\[ \frac{V_{02}}{V_i} = \frac{\left( - H_0 \cdot \frac{s}{\omega_0} \right)}{\left( 1 + \frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2} \right)} \tag{9.3}\]

The band pass shown in Figure 9.3 has its center frequency at \(1\,kHz\) as set in the requirements. Similarly to the low pass filter in Figure 9.1 and the high pass filter in Figure 9.2 the amplitude response peaks at this frequency, with its peak influenced by the quality factor.

#| label: lst-freqResponseBandpass

#| code-fold: true

#| output: false

# Behavioral Analysis Biquad Filter

import numpy as np

import matplotlib.pyplot as plt

# Initial values

f0 = 1e3 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(2, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -((1 + (s**2 / (w0**2))) * H0)

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

# Bode Diagram

fig, axs = plt.subplots(2)

#fig.suptitle("frequency response of biquad filter")

'''

# Low Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp)), label='low pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp)) * (180 / np.pi), label='low pass')

# High Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='high pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_hp)) * (180 / np.pi), label='high pass')

'''

# Band Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='band pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_bp)) * (180 / np.pi), label='band pass')

# Band Stop Filter

#axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='band stop')

#axs[1].semilogx(frequencies, (np.angle(Hs_bs)) * (180 / np.pi), label='band stop')

#axs[0].title("amplitude response")

axs[0].set_xlabel("frequency/Hz")

axs[0].set_ylabel("amplitude/dB")

axs[0].set_ylim(-50, 25)

axs[0].grid(True, which="both", ls="--")

#axs[0].legend(loc=1)

#axs[1].title("phase response")

axs[1].set_xlabel("frequency/Hz")

axs[1].set_ylabel("phase/deg")

axs[1].grid(True, which="both", ls="--")

#axs[1].legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/freqResponseBandpass.png", format="png", dpi=1000)

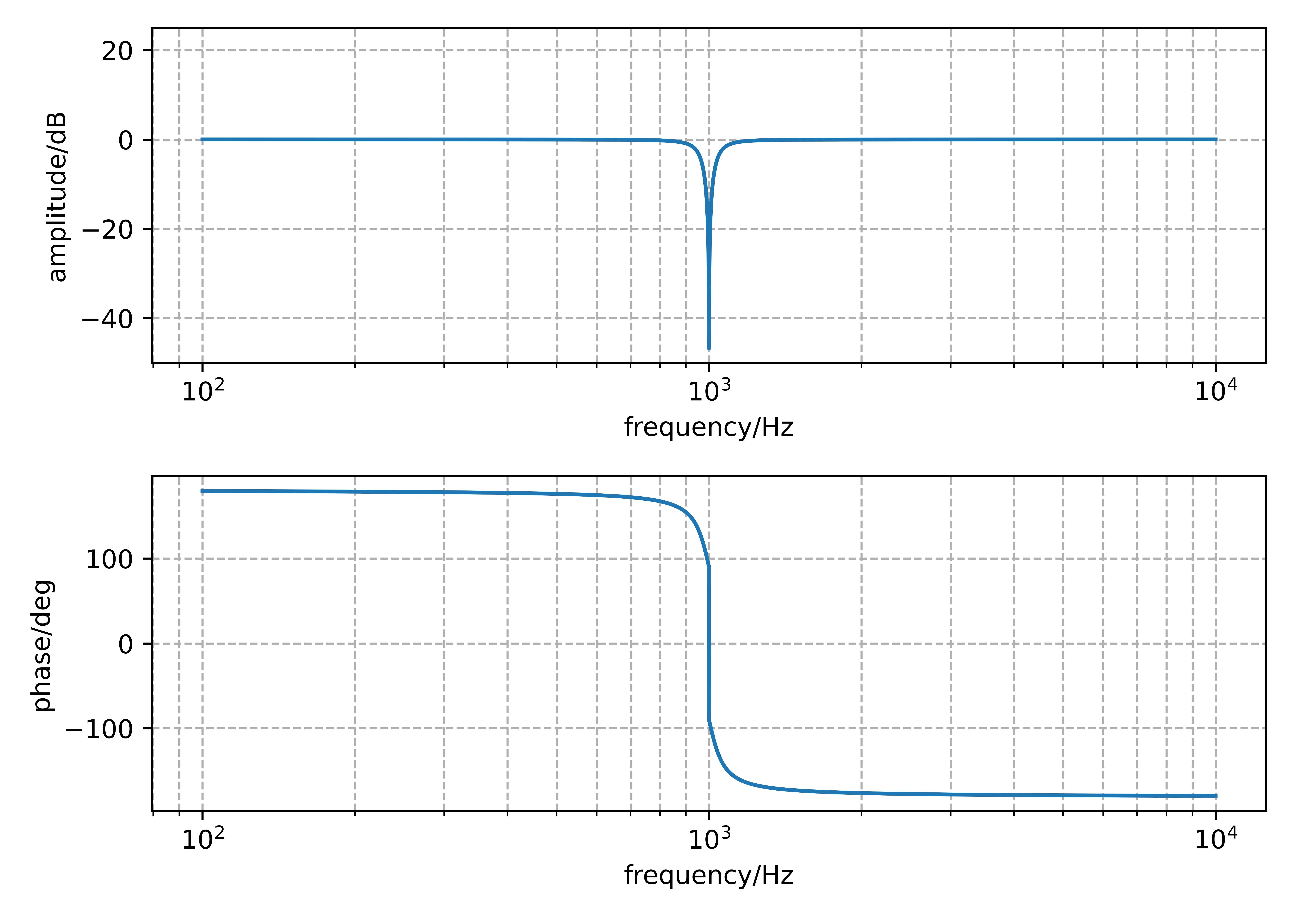

Band stop

The output for the band stop filter is marked in Figure 8.1 as \(BSF\) and in the transfer function as \(V_{04}\).

\[ \frac{V_{04}}{V_i} = \frac{\left( 1 + \frac{s^2}{\omega_0^2} \right) \cdot H_0}{\left( 1 + \frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2} \right)} \tag{9.4}\]

[12] argues that Equation 9.4 from the ASLK PRO Manual [1] is incorrect, as using that equation produces inconsistent results. Using the negated form of Equation 9.4 as seen in Equation 9.5 seems to produce the correct output. Therefore Equation 9.5 will be used for further analysis.

\[ \frac{V_{04}}{V_i} = - \frac{\left( 1 + \frac{s^2}{\omega_0^2} \right) \cdot H_0}{\left( 1 + \frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2} \right)} \tag{9.5}\]

Figure 9.4 shows the frequency response of the band stop, with its center frequency at \(1\,kHz\).

#| label: lst-freqResponseBandstop

#| code-fold: true

#| output: false

# Behavioral Analysis Biquad Filter

import numpy as np

import matplotlib.pyplot as plt

# Initial values

f0 = 1e3 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(2, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -((1 + (s**2 / (w0**2))) * H0)

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

# Bode Diagram

fig, axs = plt.subplots(2)

#fig.suptitle("frequency response of biquad filter")

'''

# Low Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp)), label='low pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp)) * (180 / np.pi), label='low pass')

# High Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='high pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_hp)) * (180 / np.pi), label='high pass')

# Band Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='band pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_bp)) * (180 / np.pi), label='band pass')

'''

# Band Stop Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='band stop')

axs[1].semilogx(frequencies, (np.angle(Hs_bs)) * (180 / np.pi), label='band stop')

#axs[0].title("amplitude response")

axs[0].set_xlabel("frequency/Hz")

axs[0].set_ylabel("amplitude/dB")

axs[0].set_ylim(-50, 25)

axs[0].grid(True, which="both", ls="--")

#axs[0].legend(loc=1)

#axs[1].title("phase response")

axs[1].set_xlabel("frequency/Hz")

axs[1].set_ylabel("phase/deg")

axs[1].grid(True, which="both", ls="--")

#axs[1].legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/freqResponseBandstop.png", format="png", dpi=1000)

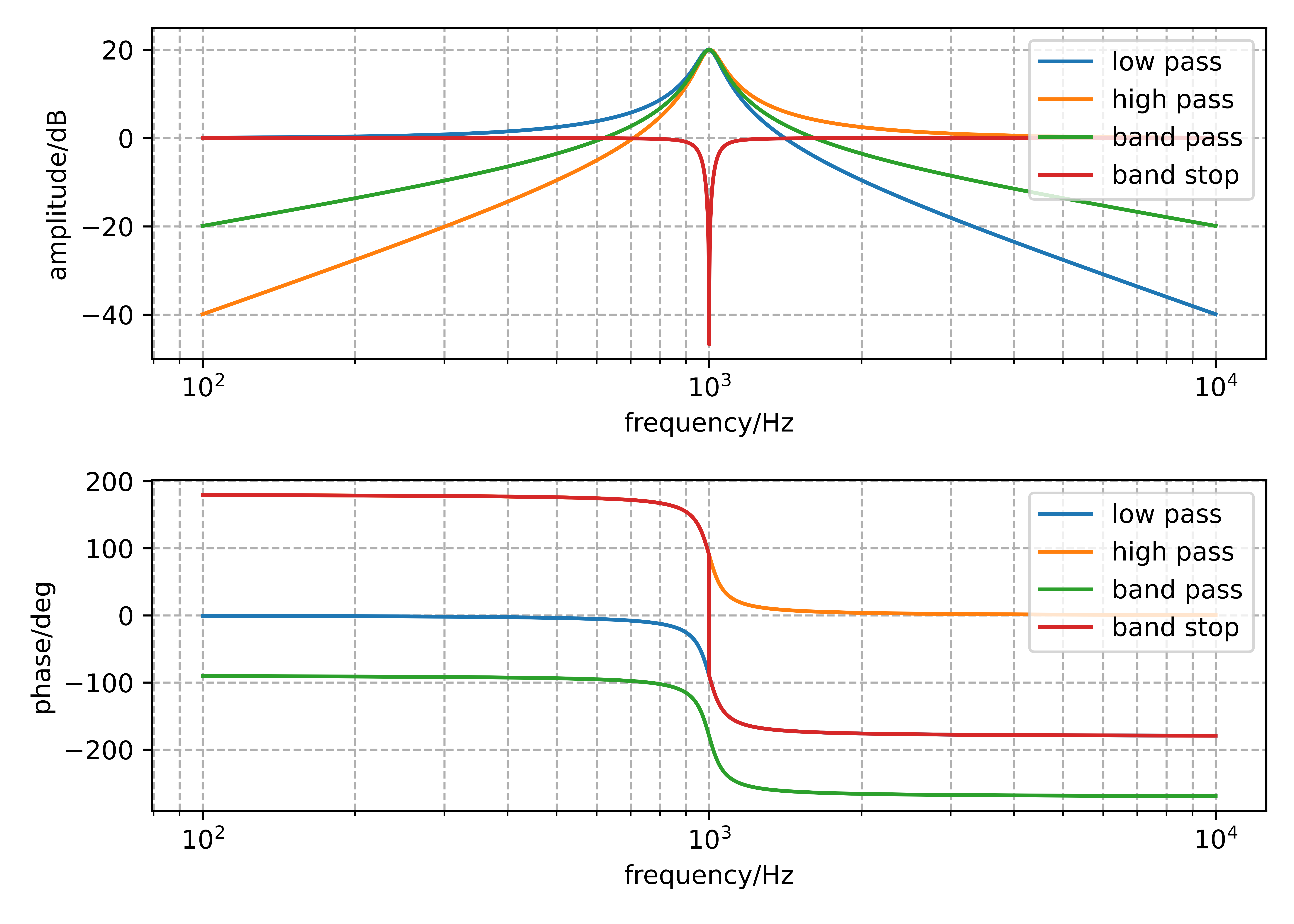

Comparison

Figure 9.5 shows all four frequency responses together in oen graph. It shows nicely that all three pass filters peak at the same freqeuncy and the same height. Comparing this plot with the one from [1] gives reason to argue that the filter design on a theoretic system level should work.

#| label: lst-freqResponseFilter

#| code-fold: true

#| output: false

# Behavioral Analysis Biquad Filter

import numpy as np

import matplotlib.pyplot as plt

# Initial values

f0 = 1e3 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(2, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -((1 + (s**2 / (w0**2))) * H0)

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

# Bode Diagram

fig, axs = plt.subplots(2)

#fig.suptitle("frequency response of biquad filter")

# Low Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp)), label='low pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_lp)) * (180 / np.pi), label='low pass')

# High Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='high pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_hp)) * (180 / np.pi), label='high pass')

# Band Pass Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='band pass')

axs[1].semilogx(frequencies, np.unwrap(np.angle(Hs_bp)) * (180 / np.pi), label='band pass')

# Band Stop Filter

axs[0].semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='band stop')

axs[1].semilogx(frequencies, (np.angle(Hs_bs)) * (180 / np.pi), label='band stop')

#axs[0].title("amplitude response")

axs[0].set_xlabel("frequency/Hz")

axs[0].set_ylabel("amplitude/dB")

axs[0].set_ylim(-50, 25)

axs[0].grid(True, which="both", ls="--")

axs[0].legend(loc=1)

#axs[1].title("phase response")

axs[1].set_xlabel("frequency/Hz")

axs[1].set_ylabel("phase/deg")

axs[1].grid(True, which="both", ls="--")

axs[1].legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/freqResponseFilter.png", format="png", dpi=1000)

9.1.2 Stability

The stability of the biquad is checked at different hierarchical levels. The first analysis considers the system from a theorectical standpoint with transfer functions, and checks if conceptual design of the biquad filter is stable. On a component level the stability of the integrators and adders is analyzed, to verify that the chosen values for resistors and capcitors do not induce oscillations through the feedback loop.

9.1.2.1 System stability

A system is stable if its impulse response is absolutley integrateable. In case of a given transfer function, this can also be checked by calculating the poles of the transfer function. If all the poles lay in the left half of the s-plane, the system is considered stable. There is a special case where single poles can lay on the \(j\omega\)-axis, on their own or in combination with poles in the left half of the s-plane. Systems which fall under that, are called marginally stable. [13]

9.1.2.2 Pole-zero plot

#| label: lst-poleZeroStability

#| code-fold: true

#| output: false

import numpy as np

import matplotlib.pyplot as plt

from scipy.signal import tf2zpk

# Given values

f = 1e3

w = 2 * np.pi * f

R = 1e3

C = 1 / (w * R)

Q = 10

H0 = 1

# Calculate w0

w0 = 1 / (R * C)

# Transfer function coefficients

a2 = 1 / w0**2

a1 = 1 / (w0 * Q)

a0 = 1

# Define transfer functions manually as (numerator, denominator) pairs

systems = {

'Low pass filter': ([H0], [a2, a1, a0]),

'High pass filter': ([H0 / w0**2, 0, 0], [a2, a1, a0]),

'Band pass filter': ([-H0 / w0, 0], [a2, a1, a0]),

'Band stop filter': ([H0 / w0**2, 0, H0], [a2, a1, a0])

}

# Function to plot pole-zero map

def plot_pzmap(num, den, title, subplot_pos):

zeros, poles, _ = tf2zpk(num, den)

plt.subplot(2, 2, subplot_pos)

plt.plot(np.real(zeros), np.imag(zeros), 'go', label='Zeros')

plt.plot(np.real(poles), np.imag(poles), 'rx', label='Poles')

plt.axhline(0, color='gray', lw=0.5)

plt.axvline(0, color='gray', lw=0.5)

plt.title(title)

plt.xlabel('$\sigma$')

plt.ylabel('$j\omega$')

plt.xlim([-1500, 1500])

plt.ylim([-10000, 10000])

plt.grid(True)

plt.legend(loc='upper right')

# Plot all systems

plt.figure(figsize=(12, 10))

for i, (title, (num, den)) in enumerate(systems.items(), 1):

plot_pzmap(num, den, title, i)

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/poleZeroStability.png", format="png", dpi=1000)

Figure 9.6 shows the pole-zero plots of all four filters, low pass, high pass, band pass and band stop. In all four plots the poles are located in the left half of the s-plane and the system can therefore theoretically be classified as stable. [3] confirms this, as the article explains that with \(Q \rightarrow \infty\) the poles of the system approach the \(j\omega\) axis and the system becomes unstable.

This analysis only considers the system as a mathematical model and as a whole. Further considerations regarding the stability of the components, integrators and adders, have to be done.

9.1.2.3 Component stability

Circuits with opamps often have feedback loops, meaning that the output of the operational amplifier is somehow connected to the inverted input of the opamp. These feedback loops become problematic when the feedback signal is in phase with the input signal, as positive feedback is created and the circuit is working as an oscillator. [14]

The stability of the non-inverting amplifier can be verified by calculating the phase reserve \(\alpha\) of the circuit. If \(f_k\) is the frequency where the feedback gain is equal to 1 and \(\varphi_k\) is the corresponding phase to that frequency, then the phase reserve is calculated by:

\[ \alpha = 180° - \varphi_k \]

For circuits to be considered stable, the phase reserve has to be positive. To reduce overshoots during the transient response, it is customary to have a phase reserve of \(\alpha > 45°\). [14]

Figure Figure 9.7 shows the transient response of a circuit with a phase reserve of \(\alpha = 5.7°\). The overshoots are clearly visible and number of the overshoots per puls are larger then the customary “one over, one under”-rule. As the phase reserve is positive, the figure shows that even though the transient response is not ideal, the oscillations are attenuated and the circuit is can be considered as stable.

In practical application, the phase reserve can be graphically determined with the help of bode diagrams. The bode diagram of the circuit with an open feedback loop is simulated, so that the frequency \(f_k\) can be read out. This is the frequency where the feedback gain is 1 or 0 dB. The corresponding frequency to that, is the phase of the feedback gain \(\varphi_k\), the difference between \(-180°\) and \(\varphi_k\) is the phase reserve \(\alpha\). [14]

For the analysis of component stability the 5t-ota design from [15] was used. Figure 9.8 and Figure 9.9 show the schematics that simulated the stability analysis for the components. In both cases the AC source was inserted in the open feedback loop and the output of the OTA was used to analyse the stability.

In the following figures Figure 9.10 and Figure 9.11 this stability analysis method was used to determine the stability over the phase reserve.

#| label: lst-stabilityAdder

#| code-fold: true

#| output: false

# Stability analysis adder

import numpy as np

import matplotlib.pyplot as plt

import sys

sys.path.insert(0, 'simulation')

import ltspy3

sd=ltspy3.SimData('simulation/stability_adder.raw',[b'v(v_out)',b'frequency'])

nvout = sd.variables.index(b'v(v_out)')

nfrequency = sd.variables.index(b'frequency')

fig, (ax1, ax2) = plt.subplots(2, 1, figsize=(10, 6), sharex=True)

ax1.semilogx(sd.values[nfrequency],20*np.log10(abs(sd.values[nvout])))

ax1.set_ylabel("Magnitude/dB")

ax1.axvline(3e5,color='red',linestyle='--')

ax1.grid(True, which="both", ls="--")

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvout], deg=True))

ax2.axvline(3e5,color='red',linestyle='--')

ax2.axhline(82.75,color='red',linestyle='--')

ax2.set_ylabel("Phase/deg")

ax2.set_xlabel("Frequency/Hz")

plt.grid(True, which="both", ls="--")

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/stabilityAdder.png", format="png", dpi=1000)

The frequency response of the adder shows a phase \(\varphi_k = 83°\), when the gain is 1. Calculation the phase reserve from that

\[\alpha_{add} = 180° - \varphi_k = 180° - 83° = 97° > 45° \]

gives a phase reserves, that indicates stability for this component.

#| label: lst-stabilityIntegrator

#| code-fold: true

#| output: false

# Stability analysis integrator

import numpy as np

import matplotlib.pyplot as plt

import sys

sys.path.insert(0, 'simulation')

import ltspy3

sd=ltspy3.SimData('simulation/stability_integrator.raw',[b'v(v_out)',b'frequency'])

nvout = sd.variables.index(b'v(v_out)')

nfrequency = sd.variables.index(b'frequency')

fig, (ax1, ax2) = plt.subplots(2, 1, figsize=(10, 6), sharex=True)

ax1.semilogx(sd.values[nfrequency],20*np.log10(abs(sd.values[nvout])))

ax1.set_ylabel("Magnitude/dB")

ax1.axvline(7e5,color='red',linestyle='--')

ax1.grid(True, which="both", ls="--")

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvout], deg=True))

ax2.axvline(7e5,color='red',linestyle='--')

ax2.axhline(68,color='red',linestyle='--')

ax2.set_ylabel("Phase/deg")

ax2.set_xlabel("Frequency/Hz")

plt.grid(True, which="both", ls="--")

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/stabilityIntegrator.png", format="png", dpi=1000)

The stability of the integrator circuit, as seen in Figure 9.11, shows a intersection of the magnitude plot with the \(0\,dB\) line at about \(f_k = 70\,kHz\), which corresponds to a phase of \(\varphi_k = 68°\). This would leave a phase reserve of:

\[ \alpha_{int} = 180° - \varphi_k = 112° > 45° \]

Therefore the integrator would be stable.

9.1.3 Ideal Opamp

To check the behauviour of the implemented circuit against the modelled behauviour of the transfer function, the universal biquad was built as an ideal circuit with voltage-regulated current sources instead of OTAs. This simulation of the circuit verfies that the circuit implementation of the biquadratic filter with OTAs can fulfill the requirements at least in the ideal case.

Figure 9.12 depicts the schematic of an universal biquad filter, where the OTAs are idealised with voltage controlled current sources. An ac simulation of this circuit can be viewed in Figure 9.13.

#| label: lst-idealCir

#| code-fold: true

#| output: false

# plot Ideal (voltage controlled current? source) biquad

import numpy as np

import matplotlib.pyplot as plt

import sys

sys.path.insert(0, 'simulation')

import ltspy3

sd=ltspy3.SimData('simulation/biquad_univ.raw')

nvoutLPF = sd.variables.index(b'v(lpf)')

nvoutHPF = sd.variables.index(b'v(hpf)')

nvoutBPF = sd.variables.index(b'v(bpf)')

nvoutBSF = sd.variables.index(b'v(bsf)')

nfrequency = sd.variables.index(b'frequency')

fig, (ax1, ax2) = plt.subplots(2, 1, figsize=(10, 6), sharex=True)

ax1.semilogx(sd.values[nfrequency],20*np.log10(abs(sd.values[nvoutLPF])),label='lpf')

ax1.semilogx(sd.values[nfrequency],20*np.log10(abs(sd.values[nvoutHPF])),label='hpf')

ax1.semilogx(sd.values[nfrequency],20*np.log10(abs(sd.values[nvoutBPF])),label='bpf')

ax1.semilogx(sd.values[nfrequency],20*np.log10(abs(sd.values[nvoutBSF])),label='bsf')

ax1.set_xlim([10e1,10e3])

ax1.set_ylim([-40,20])

ax1.set_ylabel("Magnitude/dB")

ax1.grid(True, which="both", ls="--")

ax1.legend()

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutLPF], deg=True),label='lpf')

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutHPF], deg=True),label='hpf')

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutBPF], deg=True),label='bpf')

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutBSF], deg=True),label='bsf')

ax2.set_ylabel("Phase/deg")

ax2.set_xlabel("Frequency/Hz")

ax2.legend()

plt.grid(True, which="both", ls="--")

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/idealCir.png", format="png", dpi=1000)

Figure 9.14 and Figure 9.15 compares the system-theoretic analysis with transfer functions with the simulated idealised of the filter design with each other. Both plots show very nicely that the amplitude response as well as the phase response of all four filters match with their simulated and calculated responses.

#| label: lst-compTfIdealAmplitude

#| code-fold: true

#| output: false

import numpy as np

import matplotlib.pyplot as plt

import sys

sys.path.insert(0, 'simulation')

import ltspy3

sd=ltspy3.SimData('simulation/biquad_univ.raw')

nvoutLPF = sd.variables.index(b'v(lpf)')

nvoutHPF = sd.variables.index(b'v(hpf)')

nvoutBPF = sd.variables.index(b'v(bpf)')

nvoutBSF = sd.variables.index(b'v(bsf)')

nfrequency = sd.variables.index(b'frequency')

#behauvioural moddling with tfs

# Initial values

f0 = 1000 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(0, 5, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -(1 + (s**2 / (w0**2))) * H0

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

#mag plots

fig, axs = plt.subplots(2, 2, sharex=True, sharey=True)

ax1, ax2, ax3, ax4 = axs.flatten()

# Plotting each

ax1.semilogx(frequencies, 20 * np.log10(np.abs(Hs_lp)), label='tf')

ax1.semilogx(sd.values[nfrequency], 20 * np.log10(abs(sd.values[nvoutLPF])), label='ngspice')

ax1.set_ylabel("magnitude/dB")

ax1.set_title("low pass filter")

ax1.set_xlim([10,10e4])

ax1.set_ylim([-60,25])

ax1.grid(True, which="both", ls="--")

ax1.legend()

ax2.semilogx(frequencies, 20 * np.log10(np.abs(Hs_hp)), label='tf')

ax2.semilogx(sd.values[nfrequency], 20 * np.log10(abs(sd.values[nvoutHPF])), label='ngspice')

ax2.set_title("high pass filter")

#ax2.set_xlim([10,10e3])

#ax2.set_ylim([-40,25])

ax2.grid(True, which="both", ls="--")

ax2.legend()

ax3.semilogx(frequencies, 20 * np.log10(np.abs(Hs_bp)), label='tf')

ax3.semilogx(sd.values[nfrequency], 20 * np.log10(abs(sd.values[nvoutBPF])), label='ngspice')

ax3.set_xlabel("frequency/Hz")

ax3.set_ylabel("magnitude/dB")

ax3.set_title("band pass filter")

#ax3.set_xlim([10,10e3])

#ax3.set_ylim([-40,25])

ax3.grid(True, which="both", ls="--")

ax3.legend()

ax4.semilogx(frequencies, 20 * np.log10(np.abs(Hs_bs)), label='tf')

ax4.semilogx(sd.values[nfrequency], 20 * np.log10(abs(sd.values[nvoutBSF])), label='ngspice')

ax4.set_xlabel("frequency/Hz")

ax4.set_title("band stop filter")

#ax4.set_xlim([10,10e3])

#ax4.set_ylim([-40,25])

ax4.grid(True, which="both", ls="--")

ax4.legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/compTfIdealAmplitude.png", format="png", dpi=1000)

#| label: lst-compTfIdealPhase

#| code-fold: true

#| output: false

import numpy as np

import matplotlib.pyplot as plt

import sys

sys.path.insert(0, 'simulation')

import ltspy3

sd=ltspy3.SimData('simulation/biquad_univ.raw')

nvoutLPF = sd.variables.index(b'v(lpf)')

nvoutHPF = sd.variables.index(b'v(hpf)')

nvoutBPF = sd.variables.index(b'v(bpf)')

nvoutBSF = sd.variables.index(b'v(bsf)')

nfrequency = sd.variables.index(b'frequency')

#behauvioural moddling with tfs

# Initial values

f0 = 1000 # Resonance frequency in Hz

w0 = 2 * np.pi * f0 # Angular frequency in rad/s

Q = 10 # Quality factor

H0 = 1 # Play around with this later

# Logarithmic frequency axis

frequencies = np.logspace(0, 4, 10000) # Frequency from 10^2 to 10^4 Hz

s = 1j * 2 * np.pi * frequencies # Laplace-Variable s = jω

############################################

# Transfer functions of Active Filters

############################################

### Numerator

# Low Pass Filter

b_lp = H0

# High Pass Filter

b_hp = (H0 * (s**2 / w0**2))

# Band Pass Filter

b_bp = (-H0 * (s / w0))

# Band Stop Filter

b_bs = -(1 + (s**2 / (w0**2))) * H0

# Denominator -> for all filters the same

a0 = 1

a1 = (s / (w0 * Q))

a2 = (s**2 / (w0**2))

den = a0 + a1 + a2

############################################

# Calculation of the transfer functions H(s)

############################################

Hs_lp = b_lp / den

Hs_hp = b_hp / den

Hs_bp = b_bp / den

Hs_bs = b_bs / den

#phase plots

fig, axs = plt.subplots(2, 2, sharex=True, sharey=True)

ax1, ax2, ax3, ax4 = axs.flatten()

# Plotting each

ax1.semilogx(frequencies, np.angle(Hs_lp, deg=True), label='tf')

ax1.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutLPF], deg=True),label='ngspice')

ax1.set_ylabel("phase/deg")

ax1.set_title("low pass filter")

ax1.set_xlim([10,10e3])

#ax1.set_ylim([-40,25])

ax1.grid(True, which="both", ls="--")

ax1.legend()

ax2.semilogx(frequencies, np.angle(Hs_hp, deg=True), label='tf')

ax2.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutHPF], deg=True),label='ngspice')

ax2.set_title("high pass filter")

#ax1.set_xlim([10,10e3])

#ax1.set_ylim([-40,25])

ax2.grid(True, which="both", ls="--")

ax2.legend()

ax3.semilogx(frequencies, np.angle(Hs_bp, deg=True), label='tf')

ax3.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutBPF], deg=True),label='ngspice')

ax3.set_xlabel("frequency/Hz")

ax3.set_ylabel("phase/deg")

ax3.set_title("band pass filter")

#ax1.set_xlim([10,10e3])

#ax1.set_ylim([-40,25])

ax3.grid(True, which="both", ls="--")

ax3.legend()

ax4.semilogx(frequencies, np.angle(Hs_bs, deg=True), label='tf')

ax4.semilogx(sd.values[nfrequency],np.angle(sd.values[nvoutBSF], deg=True),label='ngspice')

ax4.set_xlabel("frequency/Hz")

ax4.set_title("band stop filter")

#ax1.set_xlim([10,10e3])

#ax1.set_ylim([-40,25])

ax4.grid(True, which="both", ls="--")

ax4.legend()

plt.tight_layout()

#plt.show()

plt.savefig("images/sec_characterisation/compTfIdealPhase.png", format="png", dpi=1000)

10 Xschem Simulation

10.1 Environment Setup

Proper configuration of the simulation environment is crucial for accurate and reliable simulation results using Xschem within a Docker container. This section details the necessary considerations regarding path handling and Docker environment variables for a robust simulation process.

10.1.1 Absolute vs. Relative Path Handling

In integrated circuit simulations, particularly involving hierarchical netlisting used by Xschem, careful management of file paths is essential. Absolute paths were chosen to ensure consistency and reliability, as hierarchical structures in netlisting frequently generate new subdirectories during simulation processes. Using absolute paths prevents issues arising from relative paths becoming invalid when directory structures change. Relative paths, although theoretically functional, add complexity and increase the likelihood of path errors during simulations.

Therefore, all simulation paths have been consistently defined using absolute references, guaranteeing stable and predictable netlisting and simulation behavior throughout the project.

10.1.2 Docker Environment Variables Configuration

Within the Docker container environment used for simulations, specific variables require explicit and careful configuration. Key points regarding Docker environment setup include:

DESIGNS Variable: The core Docker environment variable,

$DESIGNS, is configured to reference the directoryroot/FOSS/designs. Local project paths and symbols are added explicitly to this variable to ensure accurate referencing and inclusion during netlisting.Docker Root Directory: The root directory within the Docker environment differs from that of the host operating system, specifically being located at

root/headless. This distinction requires careful handling when navigating or setting paths within Docker terminals.Terminal and Directory Awareness: Users, especially those working on Windows-based systems, need to distinguish clearly between terminal environments (native Windows, Windows Subsystem for Linux, Docker) as each has fundamentally different root directories and file path conventions. Maintaining clear awareness of these distinctions prevents file referencing errors during simulations.

These explicit configurations and considerations ensure that the Xschem simulation environment operates smoothly, predictably, and accurately throughout the project’s lifecycle.

10.2 Symbol and Netlist Preparation

Accurate preparation of symbols and netlists is fundamental for reliable integrated circuit simulations using Xschem. This section outlines the critical aspects regarding symbol definitions, classifications, netlist generation, and debugging practices to ensure proper functionality and error-free simulations.

10.2.1 Symbol Definitions and Classification (Analog Pins)

All symbols used within this simulation framework must be explicitly classified as analog components. Digital pins or incorrectly labeled pins lead to simulation failures because they are incompatible with the analog circuit simulation environment. Furthermore, each symbol must be explicitly marked as a sub-circuit rather than a primitive component. Mislabeling symbols as primitives can cause errors during hierarchical netlist processing, as the netlister expects defined sub-circuit symbols to correctly navigate the circuit hierarchy.

In this project, all symbols were thoroughly reviewed to confirm they were analog and properly labeled as sub-circuits.

10.2.2 Netlist Generation and Validation

Netlist generation in Xschem follows a hierarchical methodology. Starting from the top schematic, the netlister recursively searches for defined symbols globally. It is essential that symbol paths and local variables are correctly configured and matched explicitly in each hierarchy level. If paths or symbols are misconfigured or missing, the netlister fails to locate necessary components, leading to simulation errors.

Therefore, explicit steps were taken to ensure:

Proper global variable definitions for symbol paths.

Accurate symbol descriptions that match netlist entries.

Verification of netlists after every significant schematic modification.

Effective debugging practices strongly emphasize using plain-text editors to inspect and modify symbol (.sym) and schematic (.scm) files. The files (.spice) making direct text inspection both possible and advisable.

Adopting this debugging approach significantly enhanced the efficiency and accuracy of symbol and netlist preparation processes throughout the simulation.

10.3 OTA Circuit Integration Self-built Five-Transistor OTA

Initially, our group developed our own five-transistor OTA schematic within Xschem to gain practical insights and explore various design parameters.

Figure 10.1 shows the minimalist OTA designed during the early project phase. The circuit follows the five-transistor topology: an NMOS differential pair (M8/M3) converts the input difference into two anti-phase drain currents; a PMOS current mirror (M1/M7) then forces these currents to recombine at the single-ended node v_out, generating voltage gain of roughly \[ g_{m,\text{pair}}\bigl(r_{o,\text{M1}} \parallel r_{o,\text{M7}}\bigr) \] Biasing is supplied by the tail branch (M4→M2), where the external i_bias current is mirrored into M2.

10.3.1 Validation of Self-built OTA – unity-gain buffer

To verify large-signal behaviour the prototype OTA was configured as a unity-gain follower (Figure 10.2): v_out is shorted to the inverting input, and the non-inverting input is driven by a single rail-to-rail pulse PULSE(0 1.2 10m 1u 1u 20m 2) The stimulus holds 0 V for 10 ms, rises to 1.2 V in 1 µs, remains high for 20 ms, and then returns to 0 V. The long two-second period guarantees only one transition inside the 100 ms simulation window. A 20 µA current source on i_bias establishes the tail current, with supplies at VDD = 1.5 V and VSS = 0 V.

The essential NGSpice control block is

.control

save all

tran 100u 100m

*set filetype=ascii

set wr_singlescale

*wrdata tb_ota_tran_UGbuffer.txt v(v_out) v(v_in)

.endc

Figure 10.3 plots the resulting traces. The output (left) mirrors the input (right). The output does respond to the input change, it rises up during the pulse window, indicating the OTA is doing something. V_out lags significantly behind v_in and only reaches 1.1 V, while v_in reaches 1.2 V. The OTA as unity-gain buffer should closely track the input with only minimal offset or delay.

This indicates: - Too low gain - Insufficient bandwidth - Or incorrect biasing (e.g., not enough current to drive the output stage).

After conducting simulations and analyses, and discussing the results with the professor, the conclusion was that the five-transistor OTA provided by Prof. Pretel offered superior performance and reliability for our application. Thus, the decision was made to proceed with Prof. Pretl’s well-established OTA design.

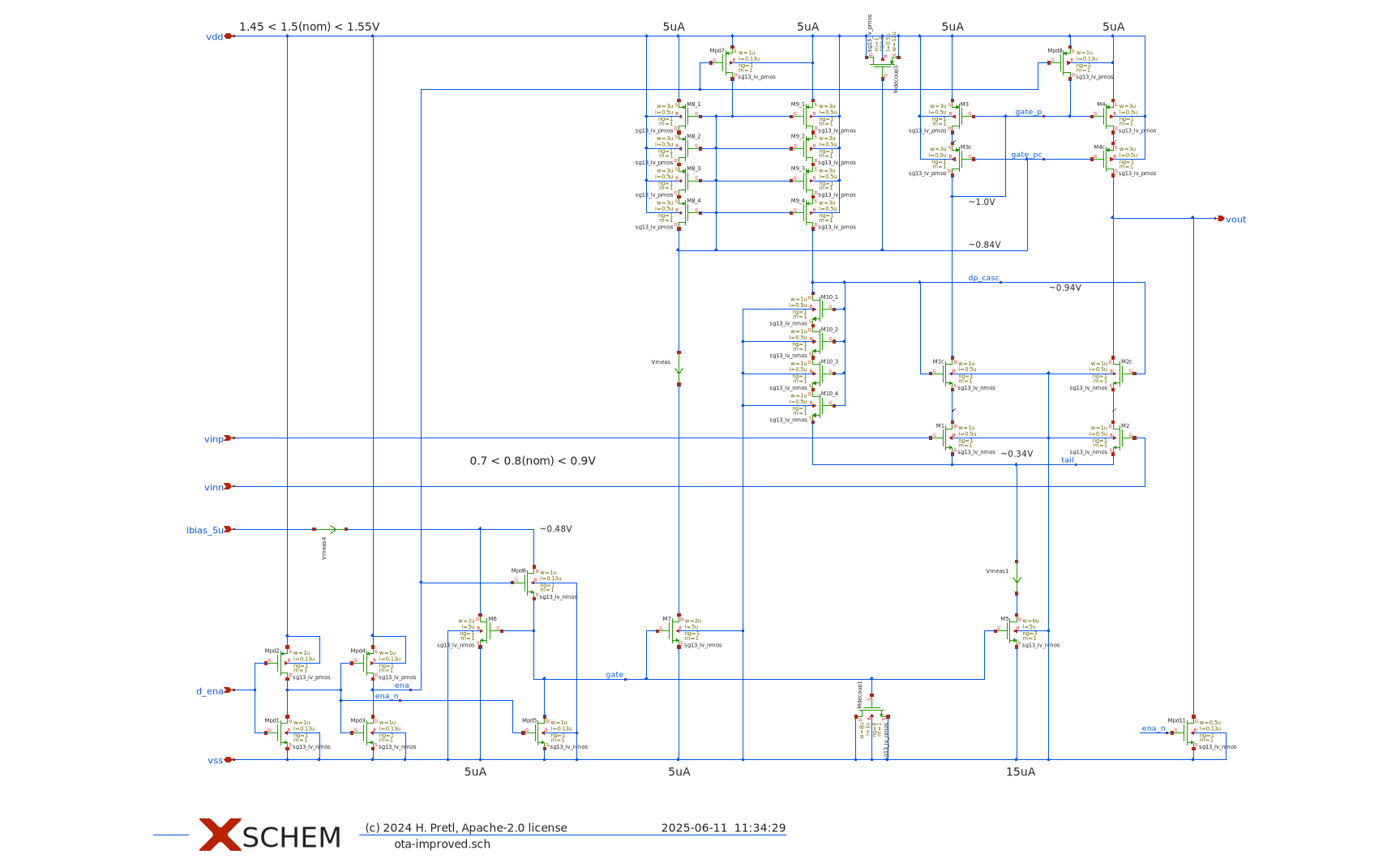

10.4 Xschem OTA Description (Five-Transistor OTA by Prof. Pretl)

Prof. Pretl’s five-transistor OTA is an optimized implementation, specifically tailored for efficient analog circuit integration using the SG13G2 CMOS process. His design, depicted in Figure 10.4, maintains simplicity while enhancing performance through thoughtful sizing and layout practices. This OTA employs a standard architecture comprising an NMOS differential input pair, a tail current source transistor, and a PMOS current mirror load. The input differential voltage is transformed by the differential pair into two opposite-phase currents, recombined by the PMOS mirror at the single-ended output node.

A dedicated transistor sets a stable bias current, ensuring predictable and robust OTA performance over varying operating conditions. Channel lengths and widths are carefully chosen to balance between adequate intrinsic gain, bandwidth, and noise characteristics. Particularly, the transistor sizes follow good IC design practices, with lengths exceeding the minimum dimensions to suppress short-channel effects and flicker noise. Bulk connections are properly handled to avoid body effects, typically by tying bulks directly to their corresponding source terminals. The accompanying layout from Prof. Pretl ( Figure 10.4) illustrates thoughtful device placement and symmetry, reducing mismatches and parasitic coupling. Furthermore, multiple finger transistors are employed effectively to optimize layout density and performance, adhering to industry-standard guidelines.

Simulations and measured data presented by Prof. Pretl validate this design as a stable, efficient, and high-performance option for analog signal processing. It exhibits superior gain and bandwidth compared to simpler OTA configurations, making it suitable for more demanding applications in integrated analog and mixed-signal circuits. Due to these advantages, our group adopted this OTA as the baseline for subsequent design and integration phases in our project.

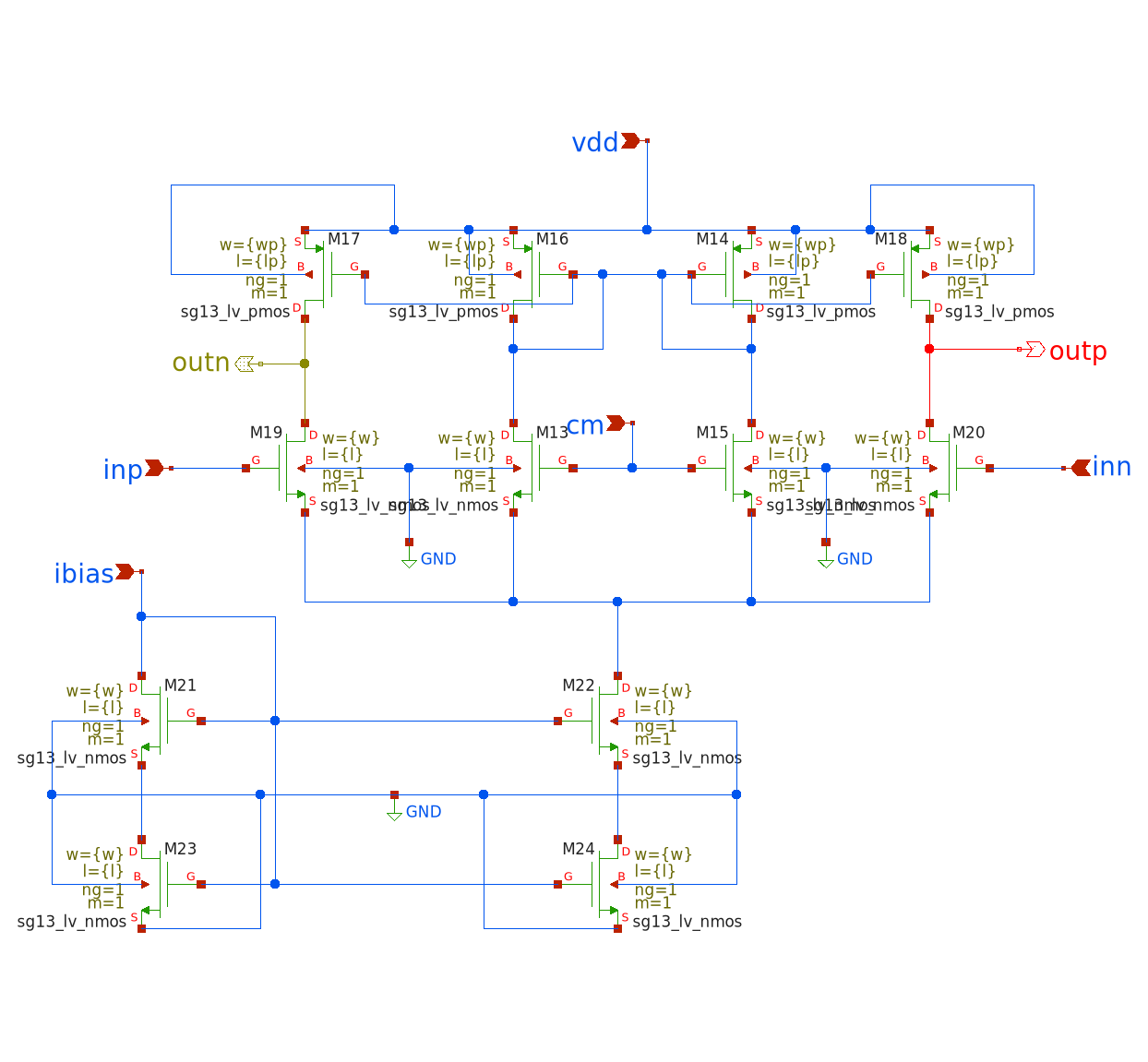

10.5 Sizing and Simulation

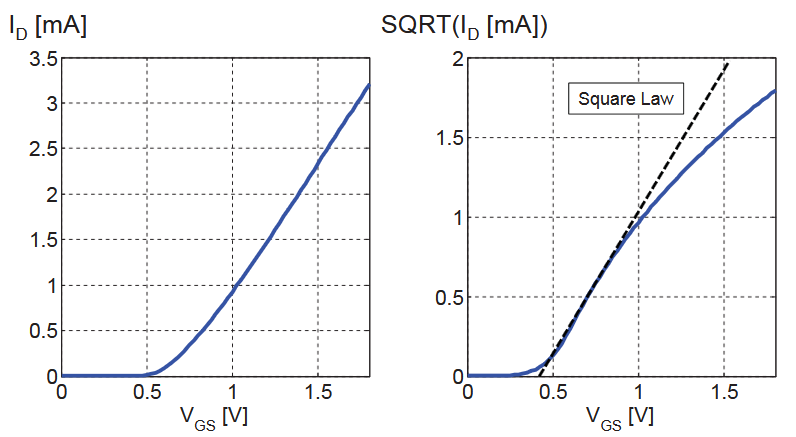

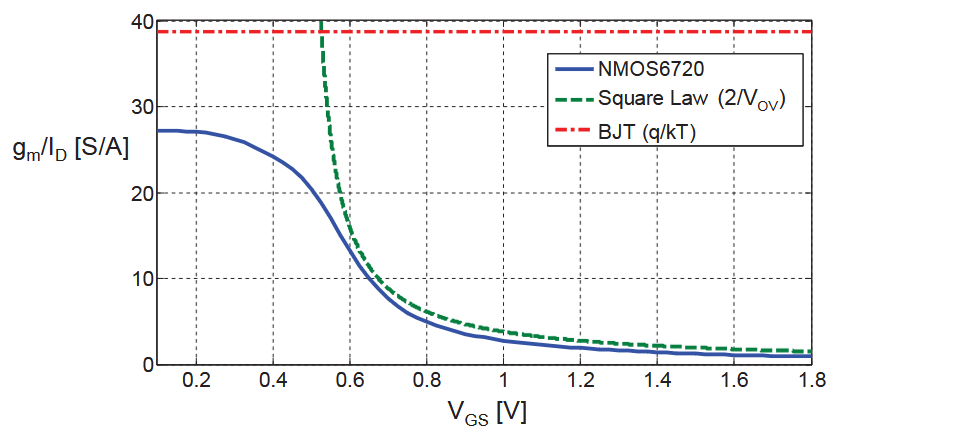

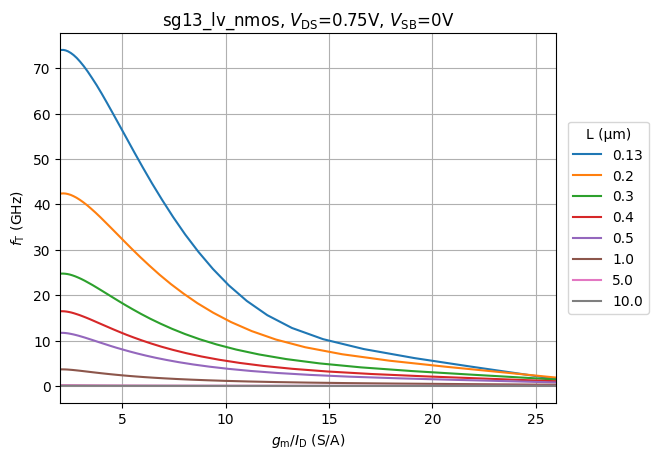

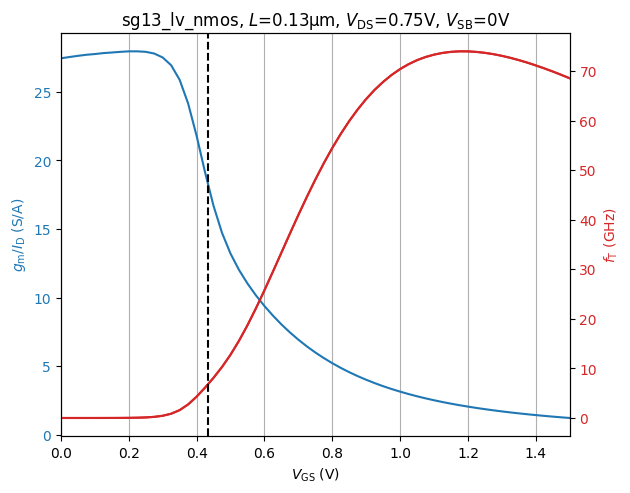

Proper transistor sizing is critical when designing an OTA for use in a biquad filter, where gain, linearity, and bandwidth all depend heavily on MOSFET dimensions. To guide the sizing process, The \(g_m / I_D\) methodology is adopted.

After experimenting with various combinations of transistor widths and lengths in simulation, we found that many trade-offs emerged between gain, speed, and voltage headroom—particularly for the cascode devices. Following Prof. Pretl’s recommendations, assigning a reduced channel length of \(L = 0.5u\) to the input differential pair and cascode devices (\(M_{1/1C}\), \(M_{2/2C}\), \(M_{3/3C}\), \(M_{4/4C}\)) to maximize speed and transconductance. Meanwhile, the tail current source transistors (\(M_5\), \(M_6\)) were given a longer channel length of \(L = 5u\) to improve matching, suppress flicker noise, and ensure robust common-mode rejection.

A constant sizing point of \(g_m / I_D = 13\) was applied across all devices, which offered a good balance between transconductance efficiency and voltage headroom. This choice ensured that even with stacked transistors, all devices remained in saturation across the intended signal swing and supply range.

Simulation results based on this sizing show that the OTA achieves an open-loop gain \(A_0 > 43\,dB\), satisfying key performance goals such as bandwidth and linear range for biquad operation. These results confirm that the selected sizing strategy works reliably within the supply voltage limits of the SG13G2 process, and is well-suited for analog signal processing tasks requiring accurate and programmable transconductance.

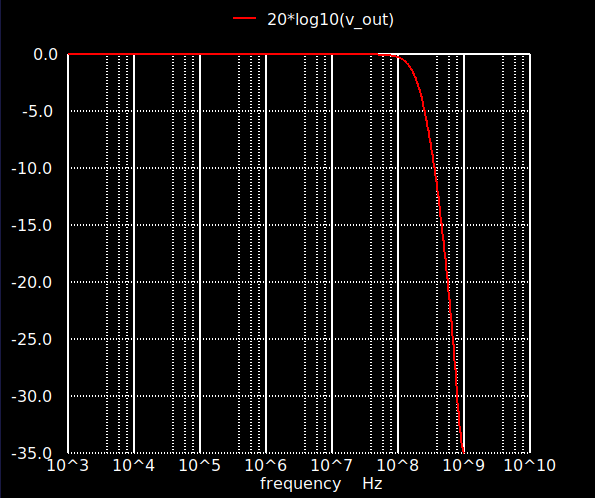

10.5.1 Small-Signal Frequency Response

To evaluate the frequency-domain behavior of the improved OTA, an AC simulation was performed using a differential testbench. The resulting magnitude response, shown in Figure 10.5, displays the classic characteristics of a low-pass amplifier.

The curve remains flat (0 dB) throughout the low-frequency range, indicating that the OTA maintains constant gain for small-signal inputs up to approximately \(f_{-3\text{dB}} \approx 80\,\text{MHz}\). This –3 dB point marks the unity-gain bandwidth of the amplifier in this configuration. Beyond this corner frequency, the magnitude begins to drop at a rate close to –20 dB/decade, indicating a dominant single-pole roll-off.

The high-frequency attenuation begins smoothly, confirming that the amplifier is well-compensated and free from peaking or signs of instability.

Overall, the OTA demonstrates a strong small-signal frequency response, offering sufficient gain-bandwidth product for its intended use in biquad filters and other analog signal processing tasks.

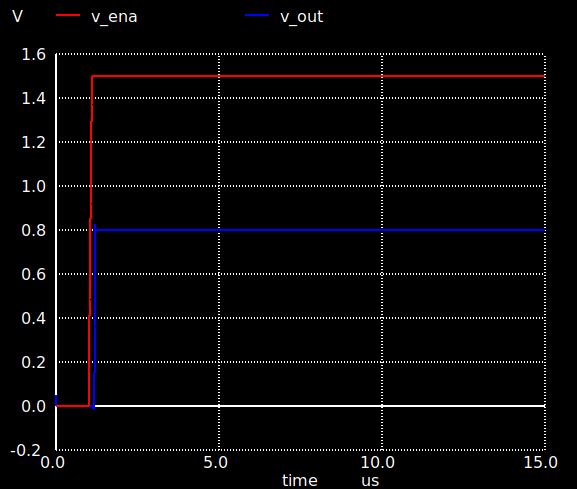

10.5.2 Large-Signal Transient Response

Figure 10.6 shows the transient simulation result of the improved OTA in response to a step input signal.

The red trace (\(v_\text{ena}\)) represents the input voltage. It exhibits a sharp transition from 0 V to approximately 1.5 V at the beginning of the simulation and remains constant for the rest of the time window.

The blue trace (\(v_\text{out}\)) shows the corresponding OTA output voltage. Immediately after the input step, the output rises to approximately 0.8 V and holds steady throughout the entire duration of the simulation (15 µs). There is no visible overshoot, ringing, or delay in the output transition, and the response appears stable and monotonic.